【导读】于芯片设计的周详系统中,复位旌旗灯号本是保障功效启动的“安全锚点”,但当复位逻辑冲破单一域的限定、超过差别域界限时,这个原本靠得住的“锚点”却可能蜕变为躲藏体系危害的“隐形裂痕”。跨复位域(RDC)问题恰是如许一种隐藏的挑战:它让功效仿真显示“一切正常”,却于芯片回片后的繁杂工况下,因复位旌旗灯号的异步开释、时序误差等触发随机功效过错,轻则致使体系异样,重则造成流片掉败。对于在寻求高靠得住性的现代芯片开发而言,成立一套靠得住的RDC签核流程是确保一次流片乐成的要害。

焦点观点:甚么是复位域与RDC?

要理解RDC,起首要明确“复位域”的观点。复位域是指由统一个异步复位旌旗灯号节制的一组寄放器或者逻辑模块。按照复位计谋的繁杂度,体系可以分为:

单复位域体系:整个芯片利用一个全局复位旌旗灯号,这是最简朴、抱负的环境。

多复位域体系:差别功效模块(如CPU焦点、DMA节制器、外设)利用各自自力节制的复位旌旗灯号。这些旌旗灯号可能异步开释,也就是开释时间差别、甚至来自差别的逻辑区块或者电源域。现代繁杂的片上体系(SoC),从手机处置惩罚器到数据中央AI芯片,险些都是繁杂的多复位域体系。

跨复位域(RDC),就是指一个旌旗灯号从一个复位域传输到另外一个复位域的路径。当这两个域的复位旌旗灯号于类型、时序或者相位瓜葛上存于差异时,RDC危害就孕育发生了。

为什么RDC是伤害的“芯片杀手”?

RDC危害轻易被轻忽,凡是缘在复位收集于年夜型设计中不像时钟收集那末繁杂,设计者轻易对于此失以轻心。然而其发生的后果与异步时钟域交织引起的后果一样致命。RDC的焦点危害源在复位的异步性,寄放器的异步复位输出因为缺少时序上的约束,使患上后续的时序电路可能激发一系列问题:

亚稳态危害:这是最经典也最伤害的问题。假如发送域的复位先激活,其输出旌旗灯号最先变化,而此时吸收域的寄放器仍处在活跃状况,当时钟沿可能刚好采到正于变化的旌旗灯号,致使寄放器输出堕入既非“0”又非“1”的亚稳态,并将这个不确定状况流传到后续电路,致使功效性过错。

复位毛刺流传:假如异步复位旌旗灯号由组合逻辑孕育发生,复位旌旗灯号可能因为组合逻辑差别输入路径延迟差别孕育发生毛刺,从而对于时序电路举行未预期的复位,致使功效紊乱。

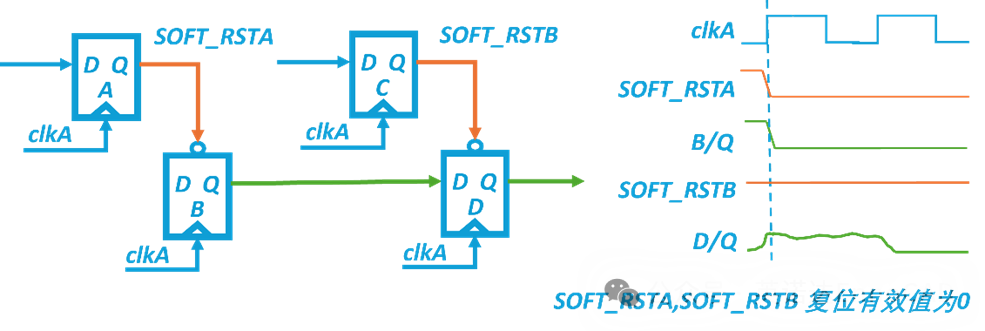

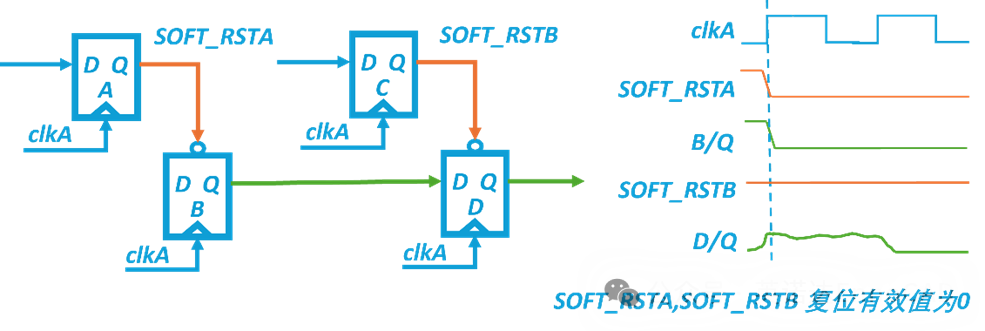

复位同步后的再会聚问题:当两个源自不异复位域或者差别步复位域的旌旗灯号,颠末差别路径(如差别长度的同步器链)同步到统一复位域后再次会聚时,可能因为复位同步路径上的延迟差异而掉去数据上的联系关系性,致使逻辑过错。

这些过错的隐藏性极强,传统的验证要领,如STA或者通例的功效仿真,很难捕获到它们,由于问题只于特定、稀有的复位时序组合下才会被触发。 一旦带有RDC问题的芯片流入市场,妨碍征象间歇性呈现,诊断及修复的成本极为昂扬。

设计实践:从源头提防RDC

优异的芯片设计不仅依赖后期验证,更于在前期的架构规避。工程师们有一系列成熟的设计准则来削减RDC危害:

首要原则-复位架构简化:于体系架构设计阶段,应只管即便削减没必要要的异步复位源。对于在统一时钟域内的模块,只管即便利用同步复位或者同一的异步复位,从底子上削减异步复位跨域路径。

电路断绝与约束技能:对于在电路中存于从“异步复位中”旌旗灯号到“未复位”旌旗灯号的路径,可以于路径上插入复位断绝单位,于发送域复位有用时期将输出钳位到已经知安全值。

复位机制保障:对于在数据流确定的电路,经由过程电路设计包管上游电路先在下流电路复位,或者者下流电路永远追随上游电路同时复位,这些复位机制能包管数据于跨复位域传输时消弭危害。

现代验证利器:RDC专用签核东西

纵然遵照了最好设计实践,于数亿门级范围的繁杂芯片中,人工审查所有潜于的RDC路径也是不成能的。这时候,专业的RDC签核东西就成了包管流片乐成的必备。英诺达EnAltius®跨域查抄东西,继撑持时钟域交织(CDC)查抄功效后,将进一步推出RDC签核查抄功效,帮忙芯片开发者快速完成RDC的验证及收敛。

总结

跨复位域问题表现了现代芯片设计中异步复位架构的繁杂性,行业内的乐成实践注解,经由过程将前瞻性的复位架构设计、体系性的复位场景治理,与强盛的主动化签核东西相联合,可以完全地消弭与复位相干的设计隐患。这不仅关乎东西的选择,更关乎一套涵盖设计、验证及调试的完备要领论的成立。只有经由过程云云严谨缜密的流程,才能确保每一一颗高度繁杂的数字芯片都能不变、靠得住地运行。

-Welcome-球速(体育科技有限公司)